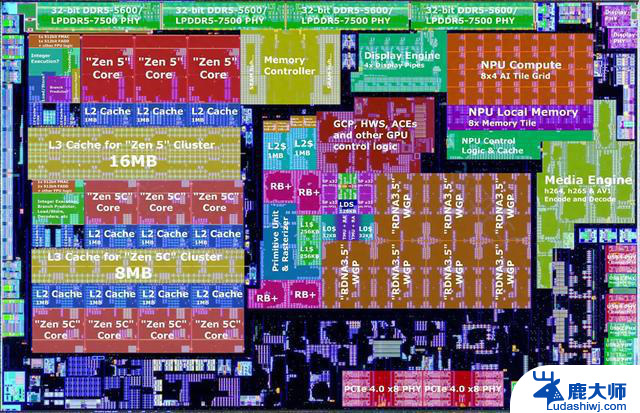

AMD新款4纳米Strix Point移动处理器透视图及注释揭秘

Nemez (GPUsAreMagic)详细注释了裸片截图。CPU 现在有 12 个核心,分布在两个 CCX 上,其中一个包含 4 个"Zen 5"核心,共享 16 MB 三级缓存;另一个包含 8 个"Zen 5c"核心,共享 8 MB 三级缓存。这两个 CCX 通过 Infinity Fabric 与芯片的其他部分相连。相当大的 iGPU 位于芯片的中央区域。它基于 RDNA 3.5 图形架构,拥有 8 个工作组处理器 (WGP),或 16 个计算单元 (CU),价值 1,024 个流处理器。其他关键组件包括 4 个渲染后端(16 个 ROP)和控制逻辑。GPU 有自己的 2 MB 二级缓存,用于缓冲向 Infinity Fabric 的传输。

与 iGPU 略有不同的是其关联组件--媒体引擎和显示引擎。媒体引擎为 h.264、h.265 和 AV1 以及几种传统视频格式的编码和解码提供硬件加速。显示引擎负责将 iGPU 的帧输出编码为各种连接器格式(如 DisplayPort、eDP、HDMI),包括硬件加速显示流压缩;而显示物理层器件则处理连接器的物理层。

NPU 是"Strix Point"的第三个主要逻辑组件。AMD 的第二代 NPU 明显大于"Phoenix"中的 NPU。它基于更先进的 XDNA 2 架构,包含 32 个人工智能引擎瓦片,可与自己的高速本地内存和与 Infinity Fabric 接口的控制逻辑对话。该 NPU 的设计满足并超越了 Microsoft Copilot+ 的硬件要求,可提供 50 TOPS 的吞吐量。

内存控制器支持双通道(160 位)DDR5(本机 DDR5-5600)和 128 位 LPDDR5(速度高达 LPDDR5-7500)。Nemez 指出,"Phoenix 2"和"Phoenix"芯片上也有这种 SRAM 缓存,但"Raphael"和"Dragon Range"中的 cIOD 内存控制器上没有。

"Strix Point"芯片的 PCIe 根复合体比"Phoenix"小,而"Phoenix"的根复合体又比"Cezanne"小。在过去的三代产品中,AMD 一直在将 PCIe 通道数减少 4 个。"Cezanne"具有 24 条 PCIe Gen 3 通道(x16 PEG + x4 NVMe + x4 芯片组总线或 GPP);而"Phoenix"则将其缩短为 20 条 PCIe Gen 4 通道(x8 PEG + x4 NVMe + x4 芯片组总线或 GPP + x4 配置为 USB4)。较新的"Strix Point"则将其进一步缩减至 16 条 PCIe Gen 4 通道(x8 PEG + x4 NVMe + x4 配置为 USB4 或 GPP)。

减少 PCIe 通道背后的理念是,"Strix Point"旨在与"Lunar Lake"对决,后者也只有 x4 的 PEG/GPP 通道,而当"Arrow Lake-H"和"Arrow Lake-HX"最终面世时,它们将遭遇 AMD 的"Fire Range"芯片,后者拥有 28 条 PCIe Gen 5 接口,甚至可以与最快的独立移动 GPU 配对。

AMD新款4纳米Strix Point移动处理器透视图及注释揭秘相关教程

- AMD 8款新处理器曝光,装机党再等等!

- PC鲜辣报:AMD发布多款新处理器显卡,14代酷睿处理器正式发布

- AMD未来移动端15~45W功耗级别单一处理器SKU消息报道

- 2024年主流移动端HX处理器性能测试:全面评测最新处理器性能表现

- 192核心384线程!AMD疯了,全球首款高性能处理器震撼发布

- AMD首款2nm芯片曝光:Zen 6架构EPYC处理器将由台积电代工

- AMD推出锐龙AI PRO 300系列商用移动处理器,领先企业AI PC新潮流

- CPU工作原理解析:从指令执行到数据处理全部揭秘

- AMD锐龙9000系列处理器售价公布,FMS 2024新品SSD大爆发:最新价格及性能一网打尽

- 2024年9月最新手机处理器性能排名!全球最强手机处理器排行榜揭晓

- 全志科技申请CPU资源调度专利,有效降低SoC系统静态功耗

- 微软Edge企业版2026年初停用旧版Adobe PDF引擎,企业必须强制迁移

- 微软Edge浏览器9月开始强制迁移Adobe PDF引擎,PDF浏览器插件需做好更新准备

- 微软AI重制雷神之锤220帧果冻人惹众怒,玩家痛批不如玩DOS版

- 微软分享Adobe for Edge引擎的新细节,即将取代旧版PDF阅读器

- 2025年4月手机性能天梯图,排行榜(手机cpu天梯图):手机处理器性能最新排名

微软资讯推荐

- 1 全志科技申请CPU资源调度专利,有效降低SoC系统静态功耗

- 2 微软Edge企业版2026年初停用旧版Adobe PDF引擎,企业必须强制迁移

- 3 微软Edge浏览器9月开始强制迁移Adobe PDF引擎,PDF浏览器插件需做好更新准备

- 4 微软AI重制雷神之锤220帧果冻人惹众怒,玩家痛批不如玩DOS版

- 5 微软分享Adobe for Edge引擎的新细节,即将取代旧版PDF阅读器

- 6 微软Xbox夏季发布会:天外世界2即将亮相,大的要来了!

- 7 CPU工作原理解析:从指令执行到数据处理全部揭秘

- 8 AMD首款2nm芯片曝光:Zen 6架构EPYC处理器将由台积电代工

- 9 2025-2031年中国AMD主板市场趋势与投资竞争力调研报告最新

- 10 英伟达RTX 5060 Ti显卡完整规格曝光:16GB显存,180W TDP详细解读

win10系统推荐

系统教程推荐

- 1 windows10flash插件 如何在Win10自带浏览器中开启Adobe Flash Player插件

- 2 台式机win10怎么调节屏幕亮度 Win10台式电脑如何调整屏幕亮度

- 3 笔记本电脑怎样设置密码开机密码 如何在电脑上设置开机密码

- 4 笔记本键盘不能输入任何东西 笔记本键盘无法输入字

- 5 苹果手机如何共享网络给电脑 苹果手机网络分享到台式机的教程

- 6 钉钉截图快捷键设置 电脑钉钉截图快捷键设置方法

- 7 激活windows7家庭普通版密钥 win7家庭版激活码序列号查询

- 8 wifi有网但是电脑连不上网 电脑连接WIFI无法浏览网页怎么解决

- 9 适配器电脑怎么连 蓝牙适配器连接电脑步骤

- 10 快捷删除是哪个键 删除快捷键ctrl加alt